Generally microprocessor alone is not a self-sufficient system. Instruction Set Architecture of 8051 It requires other components like memory and input/output devices to form a minimum workable system. Intel corporation decided to integrate a microprocessor along with I/O ports, minimum memory, programmable timer in a single package. This self- sufficient device is called microcontroller. Thus a microcontroller is a microprocessor with integrated peripherals. Instruction Set Architecture

Microcontroller is digital IC fabricated by using VLSI (Very Large Scale Integration) technology. It contains serial and parallel I/O ports, RAM and ROM types of memory. Timer/Counters, Interrupt controls etc.

Microcontroller is a complete Microcomputer on a single chip.

Advantages of microcontroller

- As the peripherals are integrated into a single chip, the overall system cost is very low.

- The product is of a small size as compared to the microprocessor based system and is thus very handy.

- The system design now requires very little efforts and is easy to trouble shoot and maintain.

- As the peripherals are integrated with a microcontroller the system is more reliable.

- Though a microcontroller may have on chip RAM, ROM and I/O ports, additional RAM, ROM and I/O ports may be interfaced-externally if required. Instruction Set Architecture

- The microcontroller with on chip ROM provide a software security feature.

- All these features are available in a 40 pin package as in an 8 bit processor.

Features of Microcontroller

- 8ry bit CPU

- On chip oscillator and clock circuitry

- 32I/O lines

- 64 Kbyte address space for external data memory

- 64Kbytes address space for external program memory

- Two number of f16 bit timer/counters

- A five source interrupt structure with two priority levels

- Full duplex serial port

- Boolean processor.

Disadvantages of microcontroller

- Learn large instruction set

- Limited calculation procedure

- Fixed programming technique to control machine.

Applications of microcontroller

- Small business system g) Telephones

- Office automation h) Washing machines

- Entertainment i) Xerox copier

- Traffic control j) Electronic toys

- Television and VCR k) Microwave ovens

- Clocks radios l) Automobiles

Comparison of Microprocessor and Microcontroller

When data is moved to SBUF, it goes to transmit buffer, where it is held for serial communication. When data is moved from SBUF, it comes from the receive buffer.

- Timer registers: Register pairs (TH0, TLO) and (TH1, TL1) are the two 16-bit counting registers for Timer/Counters 0 and 1 respectively.

- Control registers: The special function registers IP, IE, TMOD, TCON, SCON, and PCON contain control and the status information for interrupts, timer/counters and serial port. All of these are special function registers.

- Timing and control unit: This unit derives all necessary timing and control signals required for the internal operations of the circuit. It also derives control signals required for controlling the external system bus.

- Oscillator: This circuit generates the basic timing clock signal for the operation of the circuit using crystal oscillator.

- Instruction register: This register decodes the op-codes of an instruction to be executed and gives information to the timing and control unit, and to generate necessary signals for the execution of the instruction.

- EPROM and Program Address Register: These blocks provide an on-chips EPROM and a mechanism to address it internally.

- ALU: The arithmetic and logic unit performs 8-bit arithmetic and logical operations over the operands held by the temporary registers TMP1 and TMP2. User cannot access these temporary registers.

- SFR Register banks: This is a set of special function registers, which can be addressed using their respective addresses which lie in the

The interrupt, serial port and timer circuits are controlled by the control signals generated by timing and control unit.

- ALE/PROG: The address latch enable output pulse indicates that the valid address bits are available on their pins. This pin also act as program pulse input during on-chip EPROM programming.

- EA/Vpp : External access pin, if tied low, indicates that the 8051 can address external program memory. For execution of programs in internal program memory this pin must be tied high. This pin also receives 21 Volts for programming the on-chip EPROM.

- PSEN: This program store enable pin is not activated for internal fetches. It is activated when the CPU is accessing external program memory, PSEN is activated twice every cycle.

- Part 0 (P0.0 – P0.7): Port 0 acts as an 8-bit bidirectional bit/byte addressable I/O port. This has been allotted an address in the SFR address range Port 0 acts as multiplexed address and data lines (AD0 – AD7) during external memory access. Port 0 also receives code bytes during programming of the internal EPROM.

- Port 1( P1.0 –P1.7): Port 1 acts as an l8-bit bidirectional bit/byte addressable port. It has been allotted an address in the SFR address range.

- Port 2 (P2.0 –P2.7): Port 2 acts as 98-bit bidirectional bit/byte addressable I/O port. It has been allotted an address in the SFR address range.

- During external memory access, port 2 emits higher eight bits of address (A8-A15). Port 2 also receives higher order address bits during programming on the on-chip EPROM.

- Port 3 (P3.0 –P3.7): Port 3 is an 8-bit bidirectional bit/byte addressable I/O port. It has been allotted an address in the SFR address range. The port 3pins also serve the alternate functions as listed in the table below.

| Port Pins | Alternate Functions |

| P3.0

P3.1 P3.2 P3.3 P3.4 P3.5

P3.6

P3.7 |

RXD (Serial input port)

TXD (Serial output port) INT0 (External interrupt 0) INT1 (External interrupt 1) T0 (Timer/Counter 0 external input) T1 (Timer/Counter 1 external input)

WR ( External data memory write strobe) RD (External data memory read strobe) |

XTALI and XTAL2: There is an in-built oscillator which derives the necessary clock frequency for the operation of the oscillator. XTAL1 is the input to the inverting oscillator amplifier. XTAL2 is the output from the inverting oscillator amplifier.

ALU (Arithmetic and Logic Unit)

The arithmetic and logic unit performs 8 bit arithmetic and logic operations over the operands held by the temporary registers TMP1 and TMP2. The users cannot access these temporary registers.

The various arithmetic operations performed by ALU are addition, addition with carry, subtraction with borrow, increment, decrement, multiplication and division. The addition and subtraction functions are performed in both signed and unsigned manners also. Similarly ALU can perform AND, OR, EX-OR, clear, complement and rotate logic functions. After the arithmetic and logical operations the result is stored in the destination operand.

Memory organization of 8051 – instruction set architecture

The microcontroller 805f1 has three basic memory address spaces. They are

- 64 Kbyte program memory

- 64 Kbyte external data memory

- 256 byte internal data memory

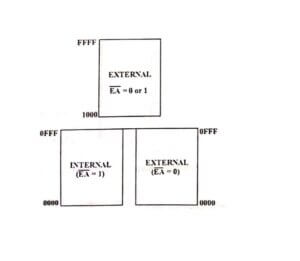

In general ROM type memories are used for program memory and RAM type memory is used for data memory. The 64 Kbyte program memory space consists of an internal and external memory portions. The data memory space also consists of an internal and an external memory spaces.

ROM (Program memory)

Program memory can only be read, not written to. There can be upto 64 Kbytes of program memory. In the ROM and EPROM versions, the lowest 4 Kbytes are provided on-chip. In the ROM less versions all program memory is external (off-chip). The 64 Kbyte program memory space consists of an internal and external memory portions. The memory map structure of program memory is shown in the table.

In microcontroller 8051, the lower 4 Kbytes of program memory can be placed either in the on-chip ROM or in an external ROM. This selection is made by strapping the EA pin to either Vcc (1) or Vss (0). I the EA pin is held high, the program fetches to addresses 0000H through 0FFFH are directed to the internal ROM. Program fetches to addresses 1000H through FFFFH are directed to the external ROM.

All the bytes in the lower 128 can be accessed by either direct or indirect addressing. The SFRs are accessed by only direct addressing.

The CPU generates RD and WR signals as needed during external RAM accesses. There can be up to 64 Kbytes of external data memory. Memory addresses can be either 1 or 2 bytes wide. Only indirect addressing can be used for accessing external data memory. In one byte addresses, the location is indirectly specified either in register RO or R1, which is specified as @Ri. In two byte addresses, the location is indirectly specified in register DPTR, specified as @DPTR.

In the external data RAM accesses, the accumulator is always the destination or source of the data. The external RAM is activated only during the execution of a MOVX instruction.

Internal RAM memory map – instruction set architecture

The internal data memory of l8051 microcontroller is divided into two physically separate and distinct blocks. They are 128 bytes of internal RAM area and the 128 bytes special function register (SFR) area. The memory map of internal RAM is shown in the image. Instruction Set Architecture

The 128 bytes internal RAM is again subdivided into three distinct areas. They are

Bank Register area: Microcontroller 8051 has four number of register banks, each contains 8 registers. They occupy the locations 0 through 31 in the lower RAM area. Their addresses are ranging from 00H to 1FH. The four register banks are numbered 0 to 3, and the eight registers are named R0 to R7. Each register can be addressed by its name (when its bank is selected) or by its RAM address. Bits RS0 and RS1 in PSW SFR determine which bank of register is currently used.

Bit and Byte addressable locations: The next 16 bytes, locations 32 through 47 are bit and byte addressable locations. They form a total of 128 bit addressable locations. These 16 byte locations may be specified by its bit address of 00H to 7FH, or byte address from 20H to 2FH.

Only byte addressable locations: The next 80 bytes, locations 48 through 127 contain only byte addressable locations. Their byte addresses are ranging from 30H to 7FH. It is called general purpose RAM area.

Special function registers – instruction set architecture

The microcontroller 8051 has a family of special purpose registers called special function registers. There are a total of 21 special function 8-bit registers. Among them, there are 11 registers are byte and bit addressable registers. They Acc(A),B, PSW,P0, P1,P2, P3,IP, IE, TCON and SCON. The remaining 10 registers, namely SP, DPH, DPL, TMOD, TH0, TL0, TH1, TL1, SBUF and PCON registers are only byte addressable registers, they are not bit addressable. The register DPH and DPL are higher and lower bytes of a 16-bit register DPTR (Data Pointer). This register is used for accessing external data memory. Instruction Set Architecture

The registers TH0 and TL0 are the higher and lower byte registers of 16-bit timer/counter register T0. Similarly, TH1 and TL1 are the higher and lower byte registers of 16-bit timer/counter register T1. The four port latches are represented by P0, P1, P2 and P3.

The TMOD and TCON registers are used for timer/counter operations. The IP and IE registers are used for interrupt operations. The SCON, SBUF and PCON registers are used for serial communication. The PCON register is also used for setting the power mode of 8051.

The list of SFR names and their byte and bit addresses are shown in the table below. The unused locations in SGRs (80H to FFH) are reserved and must not be used by the 8051 programmer. The SFR can be accessed by their names Instruction Set Architecture (which is much easier than by their addresses).

CV (Carry flag)

In an arithmetic operation when a carry is generated, the CY flag is set, otherwise it is reset. The carry flag also serves as a borrow flag for subtraction.

AC (Auxiliary Carry flag)

In an arithmetic operation either when a carry is generated from digit D3 and passed on to digit D4 or a borrow is generated from bit D4 to bit D3, the AC flag is set, otherwise it is reset.

OV (Overflow flag)

In an arithmetic operation, when a carry is generated either from bit D7 or bit D6, the OV flag is set, otherwise it is reset.

P (Parity flag)

If the result of an operation has an odd number of 1s, the party flag is set, otherwise it is reset.

Stack

Stack is a random access memory. The stack may reside anywhere in the on-chip RAM. The stack memory is pointed by a 8-bit register called Stack Pointer. SP is an only byte addressable SFR register. The stack memory is used by either programmer or microcontroller.

During the execution of CALL instructions, the microcontroller automatically stores the content of program counter in the stack memory. Similarly, by using the PUSH instruction, the programmer can store the content of any direct addressable location in the stack memory.

Timer/Counters

Microcontroller 8051 has two 16-bit timer/counter registers. They are timer 0 and timer 1.Both can be configured to operate either as timers or event counters.

In the timer function, the register is incremented every machine cycle. That means, in timer operation it counts the machine cycles. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency (fosc/12).

In the counter function, the register is incremented in response to “1 to 0” transition at its corresponding external input is sampled during S5P2 of every machine cycle.

When the samples show a high in one machine cycle and a low in the value appears in the register during S3P1 of the cycle following the in which the transition was detected. Since it takes atleast2 machine cycles (24 oscillator periods) to recognize a “1 to 0” transition. The maximum count rate is 1/24 of the oscillator frequency (fosc/24).

The TMCO, TCON, TH0,TL0, TH1 AND TL1 special function registers are used in Timer/Counter functions.

Interrupts – instruction set architecture

Interrupts are the control signals, used for getting the immediate attention of the microcontroller. When an interrupt occurs, the microcontroller stops the execution of main program and its control is immediately transferred to its corresponding service subroutine. The microcontroller 8051 provides 5 interrupt sources. They are

When an external interrupt is generated, the flag that generated is cleared by the hardware when the service routine is vectored to only if the interrupt was transition activated. If the interrupt was level activated, then the external requesting source will control the request flag, rather than on-chip hardware.

Timer 0 and Timer 1 interrupts are generated by TF0 and TF1 in TCON register, which are set by a rollover in their respective timer counter register. When a timer interrupt is generated, the flag that generated is cleared by the on-chip hardware when its control is transferred to the corresponding service subroutine.

The serial port interrupt is generated by the logical OR of RI and TI (in SCON register). Neither of these flags are cleared by hardware when the service routine is vectored to. The service routine will normally have to determine whether it was RI or TI that generated the interrupt, and the bit will have to be cleared only in software.

All of the bits that generate interrupts can be set or cleared by software, with though it had been set or cleared by hardware. Instruction Set Architecture That is, interrupts can be generated or pending interrupts can be cancelled in software.

Serial port

The serial port is full duplex, meaning that it can be transmitted and received data simultaneously. It is also a receive buffered, meaning that it can commence reception of a second byte before a previously received byte has been read from the receive register. Instruction Set Architecture The serial port receive and transmit registers are both accessed at special function register SBUF.

INSTRUCTION SET OF 8051

All family of MCS51 microcontroller support an identical instruction set. This instruction set is optimized for control applications. It provides a variety of fast addressing modes for accessing the internal RAM, to facilitate byte operations on small data structures. The instruction set provides extensive support for one-bit variables, as a separate data type, allowing direct bit manipulation in control and logic systems.

The MCS51 instruction set includes 111 instruction, 49 of which are single byte, 45 two byte and 17 three byte instructions. The instruction op-code format consists of a function mnemonic followed by destination and source operand fields. The field specifies the data byte and addressing mode(s) to be used.

The instruction set of 8051 is divided into 5 functional groups. They are.

Data transfer instructions

Arithmetic instructions

Logical instructions

Control transfer instructions

Bit manipulation instructions.

Importance terms used in instructions for specifying addressing modes

Rn – Registers R0 – R7 of the currently selected register bank.

Branching Instructions

The JUMP, CALL and RETURN instructions used in microcontroller 8051 are used to change the control of program flow. These instructions are called branching instructions. The jump instructions are conditional and unconditional, but the call and return instructions are only unconditional.

The unconditional instructions do not specify any condition in the op-code field. In conditional control instructions, any one of the conditions is specified in the op-code field. If the specified condition is true, the control will transfer to the target address, otherwise it will execute the next instruction. In unconditional control instructions, the control is definitely transferred to the target address.

The jump instructions, transfer the program control within main program or within subroutine. The call instructions, transfer the program control from main program to subroutine, or from one subroutine to another subroutine. The return instructions, transfer the program control from subroutine to main program, or from one subroutine to another subroutine.

CALL Instructions

ACALL and LCALL are the only two Call instructions used in microcontroller 8051. Both instructions are unconditional Call instructions. These two instructions push the address of the next instruction on to the stack, and then transfer the control to the target address.